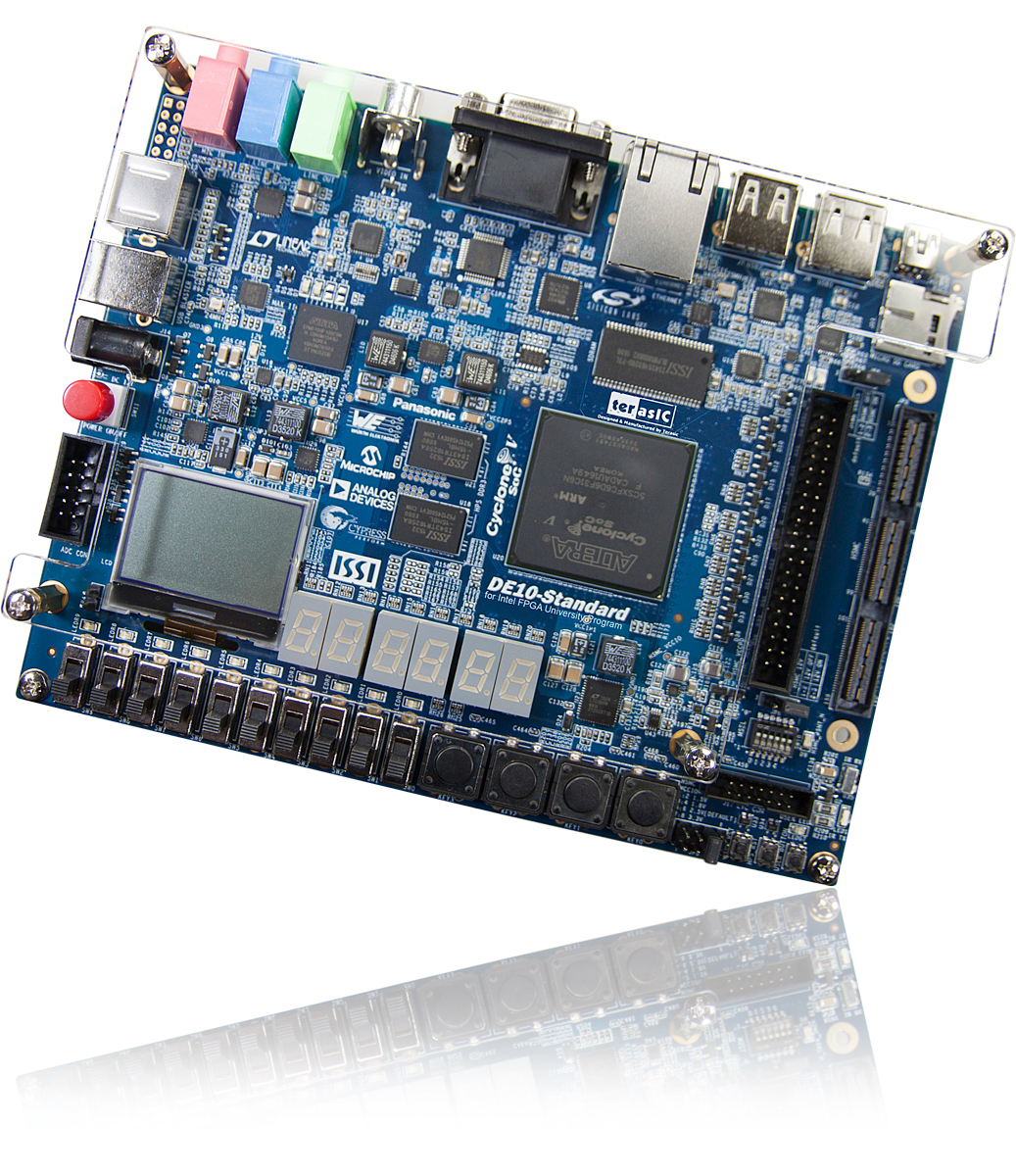

Kit FPGA DE10-Standard Altera

O Kit DE10 Standard (P0493) tem muitos recursos que permitem aos usuários implementar uma ampla gama de circuitos projetados, desde circuitos simples até vários projetos de multimídia.

Destaca-se:

Grande capacidade de reconfiguração em conjunto com um sistema de processador de baixo desempenho e baixo consumo de energia. O SoC da Altera integra um sistema de processador rígido (HPS) baseado em ARM, que consiste em interfaces de processador, periféricos e memória.

A placa de desenvolvimento padrão DE10 inclui hardware, como memória DDR3 de alta velocidade, recursos de vídeo e áudio, rede Ethernet e muito mais!

Características:

FPGA Device

• Cyclone V SX SoC—5CSXFC6D6F31C6N

• 110K LEs, 41509 ALMs

• 5,761 Kbits embedded memory

• 6 FPGA PLLs and 3 HPS PLLs

• 2 Hard Memory Controllers

ARM-Based Hard Processor System (HPS)

• 925 MHz, Dual-Core ARM Cortex-A9 MPCore Processor

• 512 KB of Shared L2 Cache

• 64 KB of Scratch RAM

• Multiport SDRAM Controller with Support for DDR2, DDR3, LPDDR1, and LPDDR2

• 8-Channel Direct Memory Access (DMA) Controller

Configuration and Debug

• Serial Configuration Device – EPCS128 on FPGA

• On-Board USB Blaster II (Normal Type B USB Connector)

Memory Device

• 64MB (32Mx16) SDRAM on FPGA

• 1GB (2x256Mx16) DDR3 SDRAM on HPS

• MicroSD Card Socket on HPS

Communication

• Two USB 2.0 Host Ports (ULPI Interface with USB Type A Connector) on HPS

• USB to UART (Micro USB Type B Connector) on HPS

• 10/100/1000 Ethernet on HPS

• PS/2 Mouse/Keyboard

• IR Emitter/Receiver

Connectors

• One 40-pin Expansion Header (Voltage Levels: 3.3V)

• One HSMC Connector(Configurable I/O Standards 1.5/1.8/2.5/3.3V)

• One 10-Pin ADC Input Header

• One LTC Connector (One Serial Peripheral Interface (SPI) Master ,One I2C and One GPIO Interface ) on HPS

Display

• 24-bit VGA DAC

• 128x64 Dots LCD Module with Backlight on HPS

Audio

• 24-bit CODEC, Line-in, Line-out, and Microphone-In Jacks

Video Input

• TV Decoder (NTSC/PAL/SECAM) and TV-In Connector

ADC

• Sample Rate: 500 KSPS

• Channel Number: 8

• Resolution: 12 bits

• Analog Input Range : 0 ~ 4.096 V

Switches, Buttons and Indicators

• 4 User Keys (FPGA x4)

• 10 User Switches (FPGA x10)

• 11 User LEDs (FPGA x10 ; HPS x 1)

• 2 HPS Reset Buttons (HPS_RST_n and HPS_WARM_RST_n)7-Segment Display x6

Sensors

• G-Sensor on HPS

Power

• 12V DC Input

Para saber mais fale conosco.